# Predictable Transactional Memory Architecture for Hierarchical Mixed-Criticality Systems

#### **DISSERTATION**

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

# genehmigte Dissertation von: Zaher Owda

vom Fachbereich Elektrotechnik und Informatik der Universität Siegen Siegen - Oktober 2016

die Promotionskommission:

Prof. Dr. Roman Obermaisser, Universität Siegen Prof. Dr. Achim Rettberg, Universität Oldenburg Prof. Dr. Roland Wismüller, Universität Siegen

Prof. Dr. Marcin Grzegorzek, Universität Siegen

Tag der mündlichen Prüfung:13 März 2017

# Predictable Transactional Memory Architecture for Hierarchical Mixed-Criticality Systems

This dissertation is submitted for the degree of

Doctor of Engineering

by

### Zaher Owda

Submitted to the Faculty of Science and Technology of the University of Siegen Siegen - October 2016

#### **Examination commission:**

Prof. Dr. Roman Obermaisser, Universität Siegen Prof. Dr. Achim Rettberg, Universität Oldenburg Prof. Dr. Roland Wismüller, Universität Siegen Prof. Dr. Marcin Grzegorzek, Universität Siegen

Defense date:13 March 2017

To my mother and the living memory of my father \*\*\*\*\*

To my beloved wife and our source of happiness  $\it Eyas$

# Acknowledgements

There is no words to utter my gratitude to all incredible people that have encouraged and motivated me during this phase of my life.

I would like to express my sincere acknowledgment to my late father, my mother and sister for their infinite love and patience. My supportive wife and lovely son *Eyas* I cannot thank you enough for the inspiration you are giving me.

I greatly appreciate the professional support and advice received from the members of my examination committee. Particularly, many thanks for Prof. Dr.-Ing. Roman Obermaisser for his guidance, assistance and constructive criticism throughout all the years of our cooperation. Moreover, I am very grateful to Prof. Dr. Achim Rettberg from the The Carl von Ossietzky University of Oldenburg for the collaboration and for his insightful feedback.

Finally, my appreciation is also extended to all the colleagues and friends with whom I had many passionate and fruitful discussions.

### **Abstract**

A transactional memory simplifies the concurrency management in multicore systems by permitting sets of load and store instructions to be executed in an atomic way. The correct results for concurrent transactions and the execution time strongly depend on the coherency potentials, rollback capabilities and strategies of the transactional memory.

A transactional memory can be implemented as a Hardware Transactional Memory (HTM), as a Software Transactional Memory (STM), or as a hybrid combination of both called Hybrid Transactional Memory (HyTM). STM is the most common implementation of the transactional memory models, which is slower but simpler and more flexible than hardware transactional memories. HyTM is an approach that combines both STM and HTM by using architectural support to accelerate particular algorithms of the STM or by allowing hardware and software transactions to operate in the same address space.

Mixed-Criticality Systems (MCSs) combine applications and subsystems at different levels of criticality on multicore systems. The development of such a safety-critical architecture requires a transactional memory architecture that guarantees the predictability, fault isolation and heterogeneity of concurrent safety-critical subsystems. Available transactional memory architectures do not support mixed-criticality at the chip level. Additionally, existing memory solutions spanning from multi-core chips to the cluster level are missing. A hierarchical transactional memory protocol is required to provide hierarchical support at all levels of the system architecture.

In this dissertation, two transactional memory architectures are proposed, namely a transactional memory for chip level architectures and a hierarchical transactional memory architecture for both multi-core chips and the cluster level.

In case of the chip-level transactional memory architecture, the predictability of the memory operations is guaranteed based on a global time base and the interarrival times of transactions. Different roll-back strategies with selective committing/aborting of requests are introduced based on the criticality of the components. This requires additional functionalities of the transactional memory such as temporal and spatial partitioning.

The hierarchical solution extends the previously mentioned properties and services to a hierarchical transactional memory protocol that guarantees the requirements for distributed MCSs. This architecture includes novel transactional memory extensions at cores, network interconnections, memory and network gateways.

The proposed transactional memory architectures introduce and exploit novel transactional memory algorithms and protocols developed for MCSs. The applied scientific and technical methods include the definition of the system and memory architecture with novel conceptual models and algorithms. A trace-based simulation framework was implemented in systemC to simulate the chip-level architecture. Additionally, this framework was extended to a co-simulation framework combining systemC with AUTOSAR for the experimental evaluation of the models and algorithms of the proposed hierarchical transactional memory architecture. Use cases from the automotive area served for the evaluation.

Better fault isolation at all levels of the chip and cluster components is obtained due to the proposed architectures. The presented solutions handle efficiently the temporal predictability at transaction level, interconnection level, memory gateway level and cluster level. For the first time, a hierarchical transactional memory–based architecture for MCS supporting chip and cluster level is presented. The proposed protocol concurrently manages the reliable execution of MCS transactions. Finally, the proposed protocol is technology independent and hides the heterogeneity of the components.

### Kurzfassung

Ein transaktionaler Speicher vereinfacht das Nebenläufigkeitsmanagement in Mehrkernsystemen, indem Sätze von Lade- und Speicherbefehlen auf atomare Weise ausgeführt werden. Die korrekten Ergebnisse für gleichzeitige Transaktionen und die Ausführungszeiten hängen stark von den Kohärenzpotentialen, Rollback-Fähigkeiten und Strategien des transaktionalen Speichers ab. Ein transaktionaler Speicher kann als Hardware-Transaktionsspeicher implementiert werden (HTM), als Software-Transaktionsspeicher (STM) oder als Hybrid-Kombination von Hardware und Software (HyTM). STM ist die häufigste und flexibelste Implementierung, jedoch langsamer als ein Hardware-Transaktionsspeicher. HyTM ist ein Ansatz, der sowohl STM als auch HTM kombiniert, indem Architekturunterstützung verwendet wird, um bestimmte Algorithmen des STM zu beschleunigen oder Hardware- und Software-Transaktionen im gleichen Adressraum zu ermöglichen.

Mixed-Criticality-Systeme (MCS) kombinieren Anwendungen und Subsysteme auf verschiedenen Ebenen der Kritikalität eines Multicore-Systems. Die Entwicklung einer solchen sicherheitskritischen Architektur erfordert eine transaktionale Speicherarchitektur, die die Vorhersagbarkeit, Fehlerisolierung und Heterogenität von gleichzeitigen sicherheitskritischen Subsystemen gewährleistet. Verfügbare Transaktionsspeicherarchitekturen unterstützen keine gemischte Kritikalität auf der Chipebene. Darüber hinaus fehlen vorhandene Speicherlösungen, die sich von Multi-Core-Chips bis auf die Cluster-Ebene erstrecken. Ein hierarchisches Transaktionsspeicherprotokoll ist erforderlich, um hierarchische Unterstützung auf allen Ebenen der Systemarchitektur bereitzustellen.

In dieser Dissertation werden zwei transaktionale Speicherarchitekturen vorgeschlagen, nämlich ein Transaktionsspeicher für Chip-Level-Architekturen und eine hierarchische transaktionale Speicherarchitektur für Multi-Core-Chips und die Cluster-Ebene.

Im Falle der transaktionalen Speicherarchitektur auf der Chip-Ebene wird die Vorhersagbarkeit der Speicheroperationen basierend auf einer globalen Zeitbasis und den Zwischenankunftszeiten von Transaktionen garantiert. Auf der Grundlage der Kritikalität der Komponenten werden unterschiedliche Roll-Back-Strategien mit selektivem Commit/Abort von Requests eingeführt. Dies erfordert zusätzliche Funktionalitäten des Transaktionsspeichers wie zeitliche und räumliche Partitionierung.

Die hierarchische Lösung erweitert die zuvor erwähnten Eigenschaften und Dienste zur Realisierung eines hierarchischen Transaktionsprotokolls, das die Anforderungen für verteilte MCS gewährleistet. Diese Architektur enthält neue Transaktionsspeichererweiterungen bei Prozessorkernen, beim Netzwerk, sowie bei Speicher- und Netzwerk-Gateways.

Die vorgeschlagenen Architekturen führen neuartige Transaktionsalgorithmen und Protokolle ein, die für MCSs entwickelt wurden. Die angewandten wissenschaftlichen und technischen Methoden umfassen die Definition der System- und Speicherarchitektur mit neuen konzeptuellen Modellen und Algorithmen. Eine trace-basierte Simulationsumgebung wurde in SystemC implementiert, um die Chip-Level-Architektur zu evaluieren. Darüber hinaus wurde dieses Framework auf eine Co-simulations Umgebung erweitert, die SystemC mit AUTOSAR kombiniertum die hierarchische transaktionale Speicherarchitektur zu evaluieren.

Ergebnisse umfassen einebessere Fehlerisolation auf allen Ebenen des Chips und der Cluster-Komponenten aufgrund der vorgeschlagenen Architekturen. Die vorgestellten Lösungen behandeln die zeitliche Vorhersagbarkeit auf der Transaktionsebene, der Netzwerkebene und der Speicher-Gateway-Ebene. Erstmals wird eine hierarchische transaktionsspeicherbasierte Architektur für MCS vorgestellt.

# **Table of contents**

| Li | st of f | igures       |                                                                | XV   |  |  |  |  |

|----|---------|--------------|----------------------------------------------------------------|------|--|--|--|--|

| Li | st of t | ables        |                                                                | xvii |  |  |  |  |

| 1  | Intr    | Introduction |                                                                |      |  |  |  |  |

|    | 1.1     | Contri       | ibutions                                                       | 3    |  |  |  |  |

|    | 1.2     | Thesis       | S Organization                                                 | 4    |  |  |  |  |

| 2  | Bac     | kgroun       | d and Basic Concepts                                           | 7    |  |  |  |  |

|    | 2.1     | Real-t       | ime Embedded Systems                                           | 7    |  |  |  |  |

|    |         | 2.1.1        | Classification of Real-time Systems                            | 10   |  |  |  |  |

|    |         | 2.1.2        | Distributed Real-time System Model                             | 12   |  |  |  |  |

|    |         | 2.1.3        | Concept of Timing in Real-time Systems                         | 13   |  |  |  |  |

|    | 2.2     | Depen        | ndability                                                      | 15   |  |  |  |  |

|    |         | 2.2.1        | Dependability Attributes                                       | 15   |  |  |  |  |

|    |         | 2.2.2        | Faults and Fault Tolerance                                     | 18   |  |  |  |  |

|    | 2.3     | Paradi       | gms of Communication                                           | 20   |  |  |  |  |

|    |         | 2.3.1        | Shared Memory and Messages-based Communication                 | 20   |  |  |  |  |

|    |         | 2.3.2        | Event Triggered vs. Time Triggered Communication               | 20   |  |  |  |  |

|    |         | 2.3.3        | Types of Communication Messages                                | 22   |  |  |  |  |

|    | 2.4     | Memo         | ory Technologies and Hierarchy                                 | 23   |  |  |  |  |

|    |         | 2.4.1        | Random-access Memory (RAM) Technologies                        | 24   |  |  |  |  |

|    |         | 2.4.2        | Memory Controller                                              | 29   |  |  |  |  |

|    | 2.5     | Transa       | actional Memory                                                | 30   |  |  |  |  |

|    |         | 2.5.1        | Types of Transactional Memory                                  | 31   |  |  |  |  |

| 3  | Ana     | lysis of     | the State-of-the-Art                                           | 35   |  |  |  |  |

|    | 3.1     | Requi        | rements for Mixed-Criticality Systems and Transactional Memory |      |  |  |  |  |

|    |         | Archit       | ectures                                                        | 35   |  |  |  |  |

**xii** Table of contents

|   |      | 3.1.1    | Real-time                                                       | 35 |

|---|------|----------|-----------------------------------------------------------------|----|

|   |      | 3.1.2    | Fault Containment                                               | 36 |

|   |      | 3.1.3    | Heterogeneity                                                   | 37 |

|   |      | 3.1.4    | Support for Hierarchical System Structures                      | 38 |

|   | 3.2  | Archit   | ectures and Solutions at Chip Level                             | 40 |

|   |      | 3.2.1    | Existing Multi-Processor System-on-a-Chip (MPSoC) Architectures | 40 |

|   |      | 3.2.2    | Existing Memory Solutions                                       | 43 |

|   | 3.3  | Cluste   | r level Distributed Memory Solutions                            | 46 |

|   |      | 3.3.1    | Distributed Shared Memory (DSM) Solutions                       | 46 |

|   |      | 3.3.2    | Transactional Memory Solutions                                  | 47 |

|   | 3.4  | Resear   | rch Gaps in the State-of-the-Art                                | 48 |

|   |      | 3.4.1    | Analysis                                                        | 48 |

|   |      | 3.4.2    | Conclusion                                                      | 49 |

| 4 | Trar | ısaction | nal Memory Architectures for Mixed-Criticality Systems          | 51 |

|   | 4.1  |          | actional Memory System-on-a-Chip (TMSoC) System Architecture .  | 51 |

|   |      | 4.1.1    | Core Architecture                                               | 52 |

|   |      | 4.1.2    | Time-Triggered Network-on-a-Chip (TTNoC)                        | 54 |

|   |      | 4.1.3    | Memory Gateway                                                  | 55 |

|   |      | 4.1.4    | External Memory                                                 | 58 |

|   |      | 4.1.5    | Mixed-Criticality Transaction Controller (MTC) Algorithms       | 58 |

|   |      | 4.1.6    | TMSoC Configuration                                             | 65 |

|   |      | 4.1.7    | Worst-case Execution Time (WCET) Analysis                       | 66 |

|   | 4.2  | Hierar   | chical Transactional Memory Architecture for Distributed MCSs   | 66 |

|   |      | 4.2.1    | Node Architecture                                               | 67 |

|   |      | 4.2.2    | Off-chip Communication Architecture                             | 68 |

|   |      | 4.2.3    | Hierarchical Transactional Memory Protocol                      | 71 |

|   | 4.3  | Fault I  | Hypothesis                                                      | 74 |

| 5 | Sim  | ulation  | Framework for Mixed-Criticality Chip Level Architectures        | 77 |

| 3 | 5.1  |          | • •                                                             | 77 |

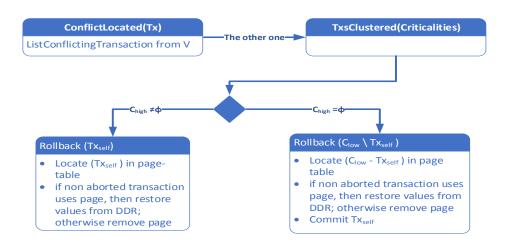

|   | 5.2  |          | nC/TLM MPSoC                                                    | 82 |

|   |      |          | ASim2 External Memory                                           |    |

|   | 5.3  |          | Example: Controller (MTC) Implementation                        | 83 |

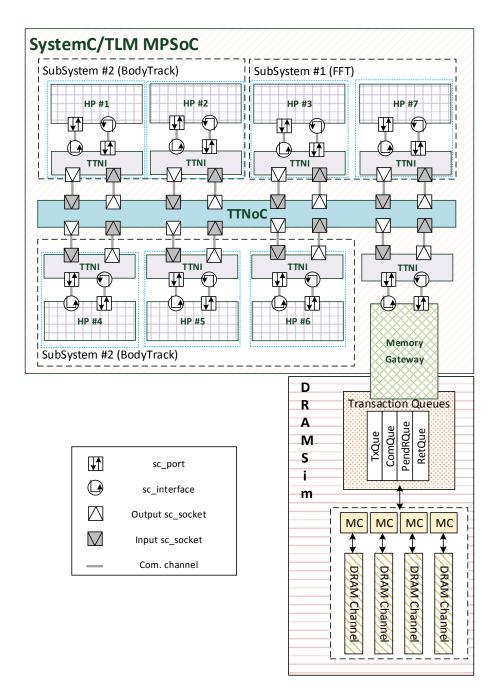

|   | 5.4  | race (   | Generation Process                                              | 84 |

Table of contents xiii

| 6  | Sim    | imulation Framework for the Hierarchical Distributed Transactional Memory |                                                           |     |  |  |  |  |  |

|----|--------|---------------------------------------------------------------------------|-----------------------------------------------------------|-----|--|--|--|--|--|

|    | Arcl   | nitectur                                                                  | e (DTMA)                                                  | 87  |  |  |  |  |  |

|    | 6.1    | Implen                                                                    | nentation                                                 | 87  |  |  |  |  |  |

|    | 6.2    | Co-sin                                                                    | nulation Coordination                                     | 90  |  |  |  |  |  |

| 7  | Eval   | luation :                                                                 | and Results                                               | 93  |  |  |  |  |  |

|    | 7.1    | Evalua                                                                    | tion of MCS Framework for Message-based and Shared Memory |     |  |  |  |  |  |

|    |        | Interac                                                                   | tions                                                     | 93  |  |  |  |  |  |

|    |        | 7.1.1                                                                     | Use-cases Description                                     | 93  |  |  |  |  |  |

|    |        | 7.1.2                                                                     | Results and Discussion                                    | 96  |  |  |  |  |  |

|    | 7.2    | Evalua                                                                    | tion of TMSoC                                             | 96  |  |  |  |  |  |

|    |        | 7.2.1                                                                     | Use-cases Description                                     | 96  |  |  |  |  |  |

|    |        | 7.2.2                                                                     | Results and Discussion                                    | 98  |  |  |  |  |  |

|    | 7.3    | Evalua                                                                    | tion of the Hierarchical DTMA                             | 100 |  |  |  |  |  |

|    |        | 7.3.1                                                                     | Use-cases Description                                     | 100 |  |  |  |  |  |

|    |        | 7.3.2                                                                     | Results and Discussion                                    | 102 |  |  |  |  |  |

| 8  | Con    | clusion                                                                   |                                                           | 105 |  |  |  |  |  |

| Re | eferen | ces                                                                       |                                                           | 107 |  |  |  |  |  |

# List of figures

| 2.1 | Cyber-Physical System                                                   | 10 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Decision making in cyber-physical systems                               | 11 |

| 2.3 | Time Division Multiple Access (TDMA)-Pulsed Data Stream [OESHK08] .     | 22 |

| 2.4 | Typical memoy hierarchy in embedded systems                             | 23 |

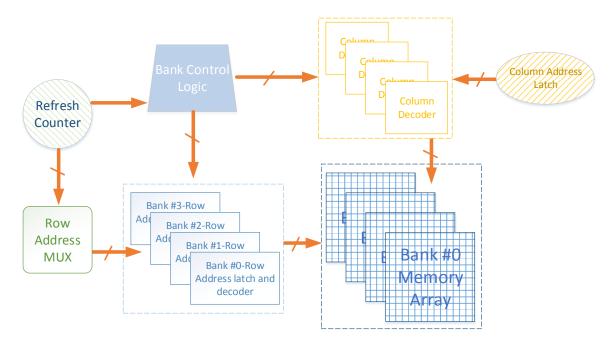

| 2.5 | DDR SDRAM memory block diagrams                                         | 26 |

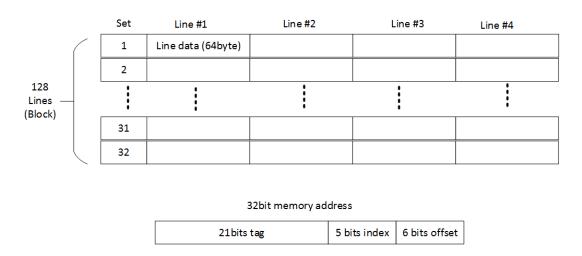

| 2.6 | 4-ways set associative cache structure (8KB cache size of 64 byte cache |    |

|     | block size)                                                             | 27 |

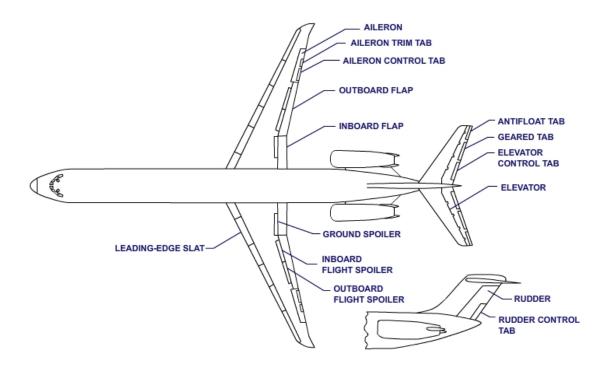

| 3.1 | DC-9-82 Flight Control Surfaces                                         | 39 |

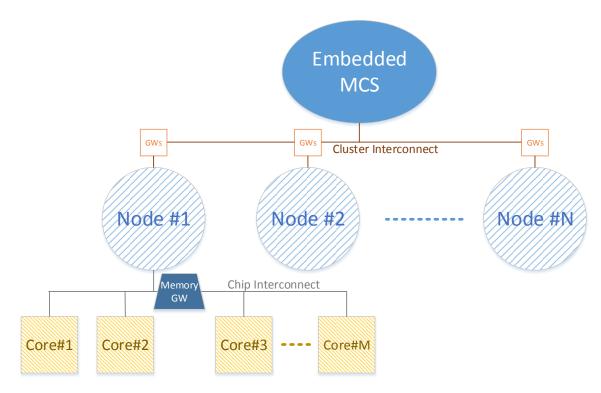

| 3.2 | Hierarchical MCS Architecture                                           | 40 |

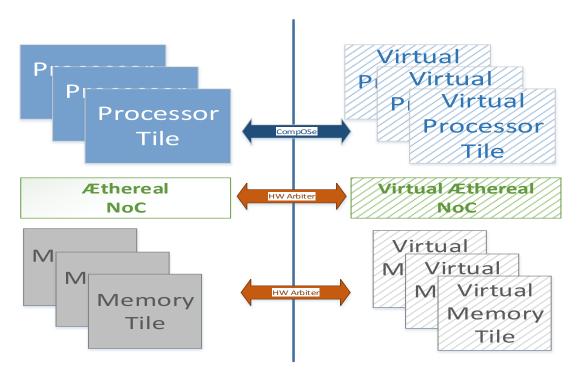

| 3.3 | CompSoC Architecture                                                    | 41 |

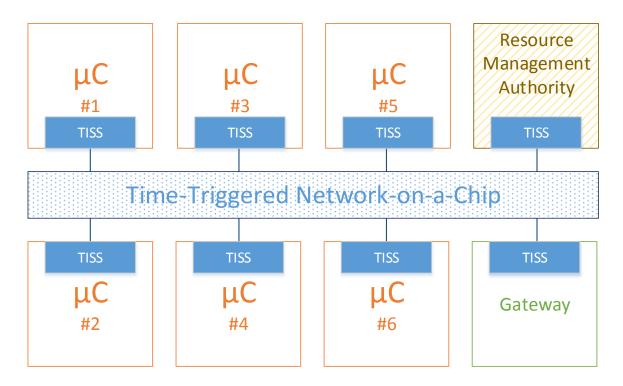

| 3.4 | Structure of Time-Triggered SoC Architecture                            | 43 |

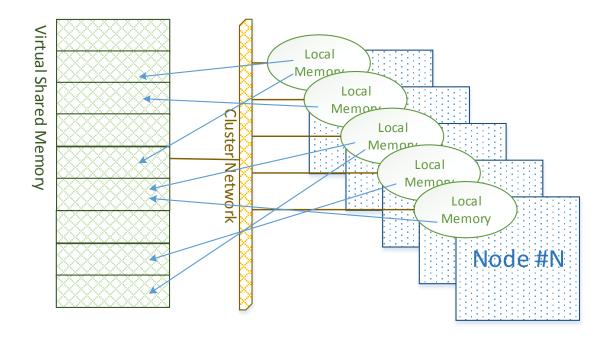

| 3.5 | Distributed Shared Memory (DSM) Architecture                            | 46 |

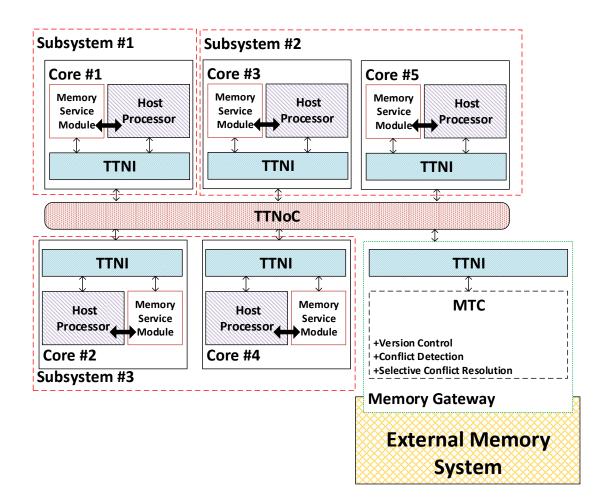

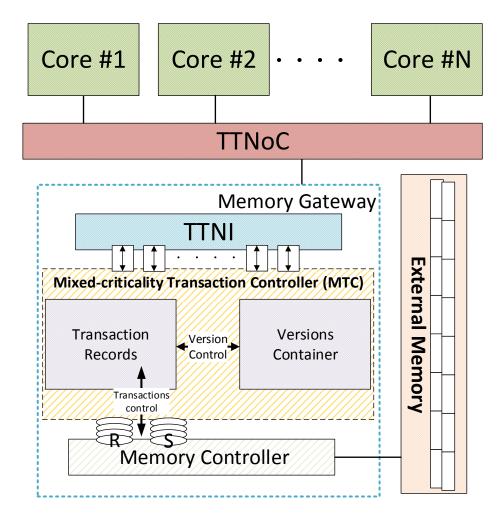

| 4.1 | The TMSoC System Architecture Overview                                  | 53 |

| 4.2 | MTC Architecture                                                        | 56 |

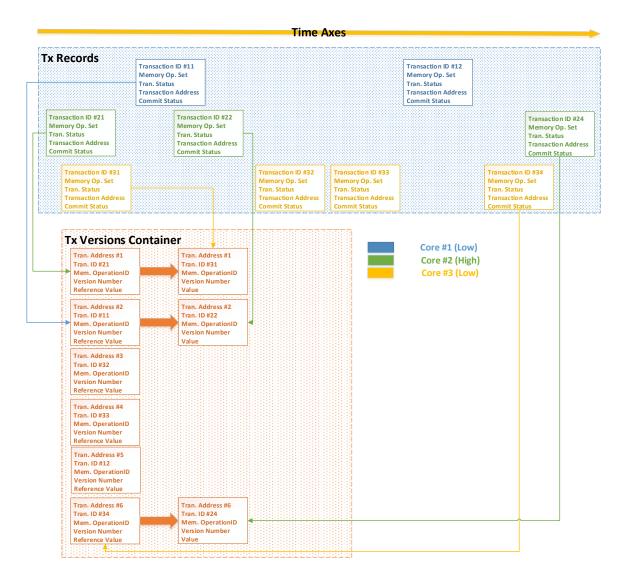

| 4.3 | Instance Representation of the MTC Containers                           | 60 |

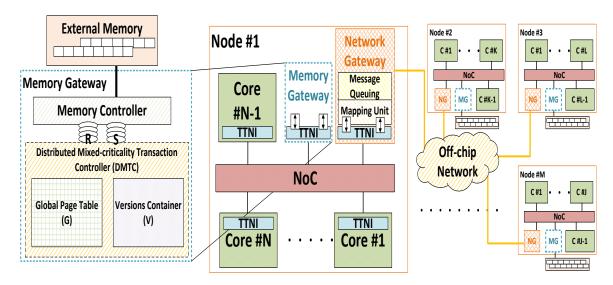

| 4.4 | The Distributed Transactional Memory Architecture (DTMA)                | 67 |

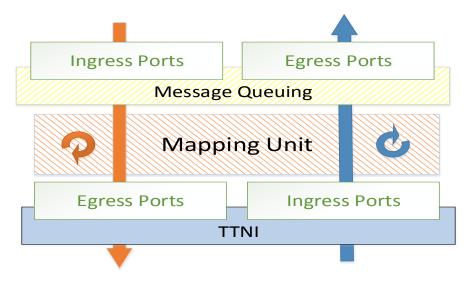

| 4.5 | Network Gateway Architecture of the DTMA                                | 69 |

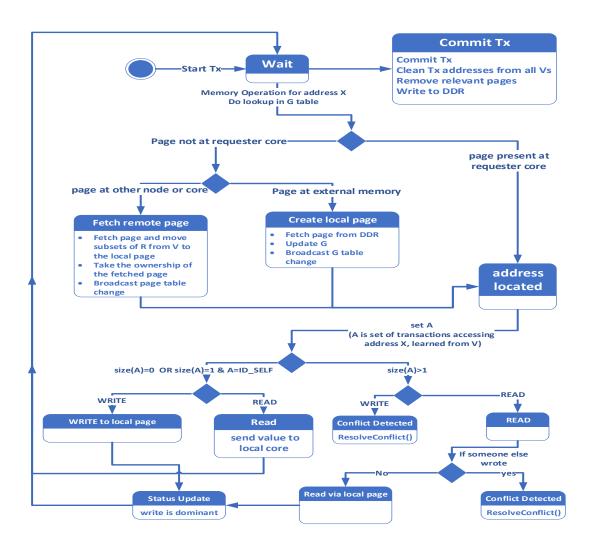

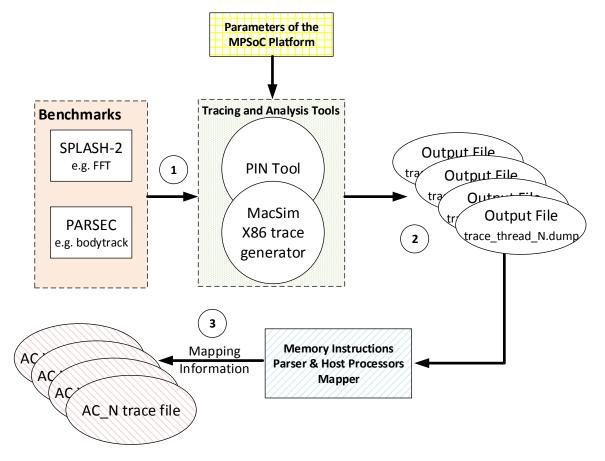

| 4.6 | Transaction Processing State Machine                                    | 72 |

| 4.7 | Criticality Based Conflict Detection State Machine                      | 73 |

| 5.1 | Simulation Framework - Implementation Model                             | 80 |

| 5.2 | Benchmarks Trace Generation Process                                     | 85 |

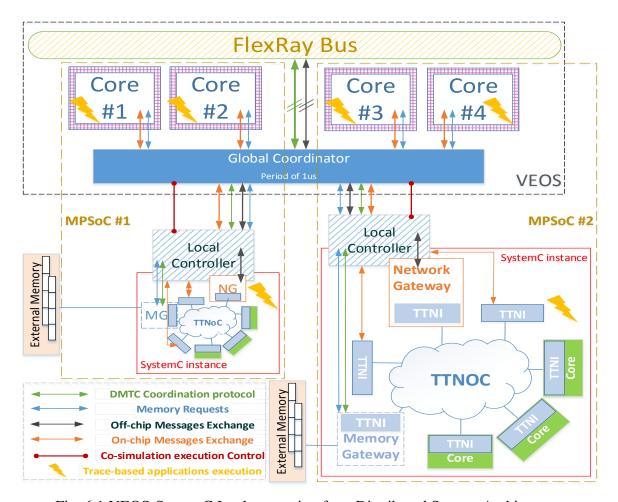

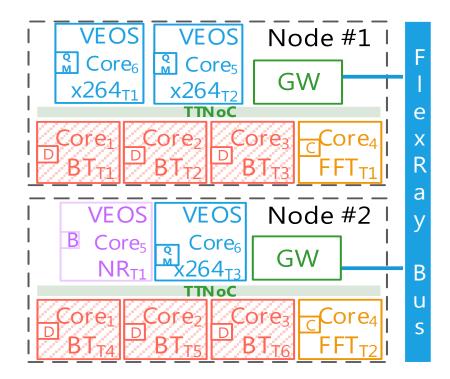

| 6.1 | VEOS-SystemC Implementation for a Distributed System Architecture       | 88 |

| 7.1 | Shared-Memory Instruction Schedule of the Use Case                      | 94 |

| 7.2 | Configuration Table for Message-based and Shared-Memory Access of the   |    |

|     | Use Case                                                                | 95 |

| kvi | List of figu | ıres |

|-----|--------------|------|

|     |              |      |

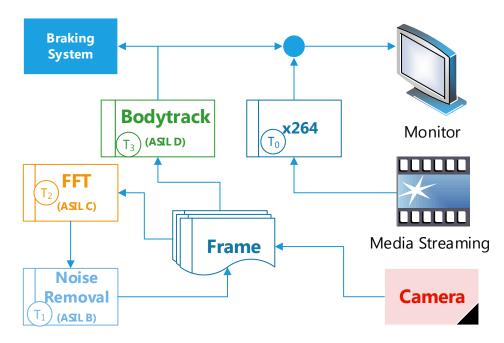

| 7.3 | Automotive Use case Scenario                     | 97  |

|-----|--------------------------------------------------|-----|

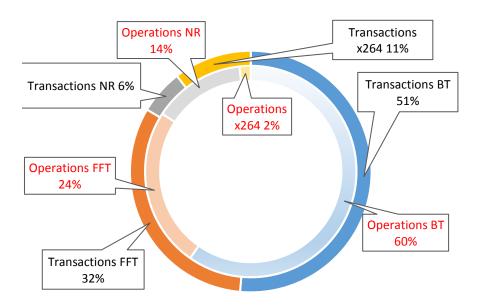

| 7.4 | Mem. Operations vs. Transactions Per Application | 98  |

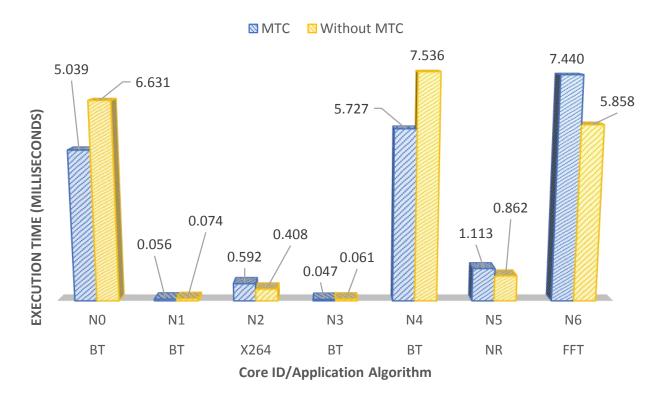

| 7.5 | Execution Time per Core                          | 99  |

| 7.6 | Distributed Automotive Use-case                  | 101 |

| 7.7 | Number of Rollbacks Performed per Core           | 102 |

| 7.8 | Execution Time per Core for both Nodes           | 103 |

# List of tables

| 7.1 | DRAMSim2 Use Case Configuration                                           | 93  |

|-----|---------------------------------------------------------------------------|-----|

| 7.2 | Overview of the Instruction Delays and Overall Completion Time in the Use |     |

|     | Case                                                                      | 96  |

| 7.3 | WCET of the ASIL tasks                                                    | 100 |

# Chapter 1

# Introduction

Mixed-criticality systems combine subsystems with different criticality levels on a shared computing platform. Mixed-criticality systems provide potential for higher reliability, energy efficiency and adaptability while also reducing the size, cost and weight of embedded systems [OOA+14a]. The increasing demand for these properties can be observed in many application domains (e.g. automotive, avionics and healthcare systems). Mixed-criticality systems are a key enabler to reduce the cabling and the number of devices in many application domains including automotive, avionic, healthcare and industrial systems [OOA+14a]. The resulting benefits include lower cost, weight and maintenance efforts due to the higher integration and the more efficient use of computational resources.

Transactional memories were initially introduced for databases and later they were proposed as a solution for concurrency control to ease parallel programming and parallel processing in multicore systems. Three types of transactional memories can be distinguished based on their implementation: hardware (e.g., 4<sup>th</sup> generation Intel processor [Int14]), software (e.g., D2STM [CRCR09] and DiSTM [KAJ+08]) and hybrid combinations of both [RMN+], [CGS+14], [BNZ08]. A transactional memory introduces atomicity of memory instructions of a complete transaction in multicore systems. In addition, it manages concurrent executions and ensures consistency of the transactions.

The use of transactional memories has been proposed in dependable embedded systems with challenges of handling faults, real-time constraints and consistency of transactional memories [FF11]. Correct execution of concurrent transactions and the WCET strongly depend on the type (i.e. eager or lazy) of the version management, conflict detection, conflict resolution services, and the available computational resources of the transactional memory [MWU13].

Transactional memories are also useful for easing the development of mixed-criticality systems, where subsystems with different safety assurance levels coexist on a shared com-

2 Introduction

puting platform. Mixed-criticality systems comprise subsystems with varying degrees of assurance and timing guarantees [Ves07b]. A prerequisite for the deployment of transactional memories in mixed-criticality systems is the prevention of unintended interference of the transactions with different criticality.

Transactional memories offer the potential to combine an optimistic operation of non safety-critical subsystems with strict real-time guarantees of safety-critical subsystems. However, a fundamental requirement in mixed-criticality systems is the segregation of subsystems with different criticality. Non safety-critical tasks should either have no effect at all on the execution times of safety-critical tasks or the effect must be bounded and known.

In case of transactional memories we can identify the following three sources of temporal interference between computational cores:

- 1. **Conflict Resolution of Transactions:** Transactional memories have the potential to cause interference between tasks due to rollbacks, which must be controlled and analyzed as a prerequisite for the deployment in mixed-criticality systems.

- 2. **Interconnect:** Segregation between applications of different criticality must be addressed at the on-chip interconnect where memory requests and data are exchanged between the computational cores and the memory gateway.

- 3. **Memory Gateway:** The memory gateway has to schedule memory requests from different computational cores. Typically, memory controllers optimize throughput, while temporal interference between cores is not addressed (e.g., bank switching).

Therefore, mixed-criticality systems require a transactional memory to provide concurrency control and timing guarantees for the subsystems by prohibiting temporal interference of the transactions in the transaction management, the interconnect and the memory controller.

Major research gaps are architectures, system models and algorithms for transactional memories in hierarchical mixed-criticality systems comprising networked multi-core chips. These systems combine two integration levels. Firstly, a multi-core processor consists of a set of computational cores that interact via an on-chip interconnect. Secondly, the cluster-level uses off-chip networks for the interconnection of several multi-core processors. A single multi-core chip is often insufficient to meet the resource requirements of large embedded applications. In addition, the failure rates of a single chip are too high to meet the reliability requirements of fail-operational systems with ultra-high dependability [SWH95] (e.g., Class A according to DO-178C [RTC11]). Hence, fault-tolerance at system level is required by exploiting redundancy with multiple independent chips.

1.1 Contributions 3

### 1.1 Contributions

This thesis introduces a mixed-criticality aware architecture, starting at the chip-level and then extending a hierarchical distributed systems. The architectures offer temporal predictability and fault isolation of the transactional memory in mixed-criticality systems. The algorithms and protocols for transaction management and conflict resolution ensure that the execution time of safety-critical applications does not depend on applications of lower-criticality. This property is significant for modular certification, where separate safety arguments are established for application subsystems with different criticality levels. In contrast, in case the conflict resolution would not prevent low-critical applications from affecting safety-critical ones, the criticality of all application subsystems would be elevated to the highest criticality level in the system.

Additionally, memory operations of the hierarchical architecture are managed in a distributed manner at the cores of different multi-core chips. This is achieved by executing a transactional-memory protocol spanning both on-chip and off-chip networks while hiding the heterogeneity of the implementation technologies. Memory pages are relocated between the local caches at cores and the external memories of the multi-core chips. In addition, commits and rollbacks are performed to ensure atomicity, consistency and isolation in the presence of memory conflicts.

The contributions of this dissertation for resolving the problem are as follow:

- A Transactional Memory System-on-a-Chip (TMSoC) architecture that is based on a deterministic Network-on-Chip (NoC). The TMSoC utilizes a transactional memory to provide segregation and fault containment at the different levels of the chip-level architecture. The architecture consists of a configurable number of cores and a memory gateway that exploits the Mixed-Criticality Transaction Controller (MTC) extension for mixed-criticality systems support.

- The Mixed-Criticality Transaction Controller (MTC) extension introduces criticalityaware algorithms that are responsible for executing so-called selective rollbacks of transactions based on their criticality.

- A hierarchical distributed architecture extends the TMSoC chip-level architecture in order to provide segregation and predictability at cluster-level. The architecture uses a transactional-memory based protocol that is spanning both on-chip and off-chip networks handling transactions based on their criticality.

- The Distributed Mixed-criticality Transactional Controller (DMTC) is deployed as a transactional-memory protocol at on-chip and off-chip network levels of the

4 Introduction

distributed architecture. This protocol hides the diversity of the components in the system ,and guarantees the criticality-aware execution of the application subsystems by executing selective rollbacks when required.

- Simulation frameworks: A fully configurable and extendable simulation framework supporting message-based and shared memory interactions has been implemented. The framework provides a trace-based simulation environment for chip-level mixed-criticality systems. Additionally, it has been extended to support distributed mixed-criticality simulations.

- Evaluation and experiments. Automotive use cases have been used to evaluate the architecture models and algorithms. The simulation framework was used to perform the experiments, which have shown that the proposed architectures and their algorithms meet the requirements including temporal predictability and fault isolation.

## 1.2 Thesis Organization

The remainder of the thesis is structured as follows.

- Chapter 2 introduces the basic concepts and provides the background knowledge used in this work. It starts with a classification of real time embedded. Afterwords, dependability attributes, and the notion of faults and fault tolerance are discussed. Next, a comparison between shared memory and message-based communication paradigms is given. The control signals for triggering interactions in these paradigms are also analyzed. The chapter ends with a presentation of the available memory technologies including memory controllers, and the notion and types of transactional memories.

- Chapter 3 provide an analysis of the state-of-the-art. It starts with the requirements for mixed-criticality systems and transactional memories. The next two sections investigates existing architectural solutions at both chip and cluster levels. The presented solutions are analyzed toward the fulfillment of the requirements. Based on this analysis, the research gaps in the state-of-the-art are highlighted to be addressed in this dissertation.

- Chapter 4 presents an architectural solution for MPSoCs that is based on a deterministic NoC and a transactional memory, known as the Transactional Memory System-on-a-Chip (TMSoC). This architecture uses the newly introduced Mixed-Criticality Transaction Controller (MTC) algorithms to guarantee the predictability and fault isolation

in mixed-criticality systems. In the second part of this chapter, a hierarchical transactional memory architecture for distributed mixed-criticality systems is defined. The introduced hierarchical architecture uses the so-called Distributed Mixed-criticality Transactional Controller (DMTC) protocol that hides the heterogeneity of the distributed components and provides a reliable memory protocol for mixed-criticality systems.

- Chapter 5 offers a trace-based simulation framework for shared memory and message-based communication in multi-core chips. The framework is dedicated to mixed-criticality system simulations based on the proposed TMSoC. It provides high abstraction levels using SystemC/TLM and it exploits DRAMSim2 for simulating the external memory of the TMSoC.

- Chapter 6 extends the earlier described framework to support the simulation of the hierarchical transactional memory architecture. This is achieved by implementing the DMTC protocol and integrating a co-simulation mechanism between the System-C/TLM multi-core simulation and the cluster level communication. The introduced co-simulation of the hierarchical framework guarantees the time integrity of the different instances with the off-chip communication simulated in VEOS/AUTOSAR.

- Chapter 7 describes three automotive use cases for the evaluation of the simulation framework and the proposed TMSoC and hierarchical transactional memory architectures. The simulation results of the use cases are presented and discussed at the end of each evaluation scenario.

- Chapter 8 concludes the thesis through a discussion of the overall results of the presented solutions.

# Chapter 2

# **Background and Basic Concepts**

The basic concepts and the required background understandings are presented in this Chapter. Starting with the notion of real-time system, and its different classifications. Then, the behavioral model of the distributed real-time system is depict. Introducing later the basic concepts of timing properties and measurements in real-time system.

Afterword, the dependability attributes and threats are illustrated to define what is a dependable system. In the next subsection, the difference between message-based and shared memory communication is presented. These paradigms of communication are also analyzed in regard to the triggering control signals in the system. Finally, we exhibit the different types of communication messages.

In the last subsections, memory technologies and hierarchy is interpreted covering the basics of this large theme. The concept of transactional memory, its architecture and types are explained at the end of this Chapter to wrap-up all required knowledge for this work.

# 2.1 Real-time Embedded Systems

A set of dependent components with distinct timing and spatial limits that are forming an entity is defined as a *system*. This includes the description of the overall system's functionalities, behavior and the interacting means with its environment represented in the inputs/outputs of the system. The system user can be a human operator or another computer system. The service delivered by a system is its behavior perceived by the user.

Several definitions for embedded systems are given in literature. An *embedded system* as defined by Steve Heath [Hea02], is a microprocessor-based system which is built to accomplish a function or a sort of functions and is not designed to be programmed by the end-user in the same manner that a personal computer is. Fundamentally, an *embedded system* comprises one or more processors, a set of memory components and a number of

peripherals to the environment. A processor consists of an instruction control unit and an arithmetic unit, which carry out instructions of a computer program by performing the basic arithmetical, logical and input/output operations of a system [Sta96].

Memory is an essential part of an embedded system. Today's systems involve different types of memories in addition to memory management and memory protection units that provide translation interfaces, partitioning and access permissions. In order to deal with the increasing complexity and performance demands of embedded systems, caches are used to provide direct and fast access to data in order to increase the performance and reduce memory access delays. Moreover, non-volatile memories (i.e. ROM memory) are used to store program code and configuration information, since even when power is removed this memory retains its content. Another type of memory that is used in embedded systems is volatile memories (i.e. RAM memory) to provide interim storage to the applications data variables that are used or computed during the execution [LS11].

Interactions and data exchange between embedded systems and their external environment is achieved through the peripherals. Dedicated operations at the *Input/Output (I/O)* ports are executed to collect data (e.g. temperature and pressure sensors), and transmit actions and signals to the system's actuators and other output devices.

Bell Telephone Laboratories and the Massachusetts Institute of Technology (MIT) initially raised the term of *real-time systems* during the Second World War, which was obviously required due to the need to improve the computational and physical time correctness of the systems. The first high speed digital computer that was able to operate in real-time was introduced by the Whirlwind project [RS80]. IBM developed a flight simulator for the American army in 1947 which was the largest computer project until the early 1950s.

The first use of the term real-time in non-military domains was in the context of real-time operating systems for airline reservation systems. SABRE was one of the first reservation systems, it was introduced for American Airlines in the year 1964. This led to the purposeful involvement of real-time software in process control for spacecraft-control and space-telemetry by the American national space programs [LO11]. During the 60s and 70s the progress at the integration levels and processing speed resulted in the enhancement of the real-time process control systems.

Moreover, a definition based on the German industry standard DIN 44300 for the real-time operations presented in Kavi [KS92] states that a *real-time operation* is an operation that meets the following conditions: all data inputs arriving to the operation shall be available any time to be processed and the operation provides its result within a given period of time. The arrival time of the data can be randomly distributed or can be already a priori determined depending on the type of the applications. For instance, in the control loop of an Anti-lock

braking system (ABS), the vehicle speed is continuously monitored and the breaking systems has to react according to the collected data. In case of skidding, the system is required to react within bounded time to avoid an accident.

Nowadays, demands for high performance in systems such as flight control, power plant control, autonomous driving and automatic train control have resulted in increasing reliability requirements not only in the value domain but also in the time domain. Such real-time systems involve more and more embedded systems with dedicated functions, control services and strict real-time constrains. Based on that, a *real-time embedded system* is defined as a system in which the correctness of its behavior depends on the computational results as well as the physical time that these results are produced with respect to the global time base [Kop13].

Real-time systems are mostly part of larger systems. Self-contained real-time subsystems that change as a function of physical time, inputs and states are called real-time clusters or Cyber-Physical Systems (CPSs).

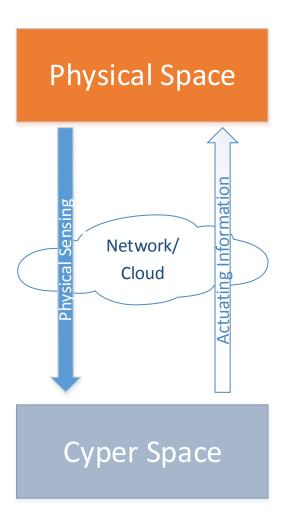

Understanding CPS can lead us to a better realization of real-time systems. As illustrated in Figure 2.1, such systems consist of two spaces that are interacting through a network or a cloud, which depends on the scale of the system. The physical space can be any real-life space such as a vehicle, a power plant, a hospital, a transportation network, etc. Furthermore, a cyber space is an artificial space that processes the collected physical inputs using the required computational resources. The cyber space includes processing units, I/Os, computer networks, etc. The resulting outputs of the cyber space are activation decisions and signals for the physical space. The resulting outputs shall lead to the correct behavior of the CPS with respect to its time restrictions on a global time base.

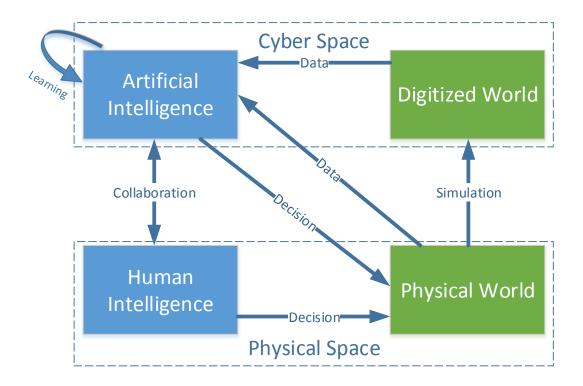

In order to take the desired decisions at any CPS, the decision making process is divided into two phases (cf. Figure 2.2). A cyber phase involves the artificial factors, and a physical phase depends on direct involvement of the human factors. The cyber space can employ artificial intelligence that is responsible for executing designated algorithms for maximizing the chances getting the desired decisions. These algorithms use the data collected from both physical and cyber (digitized) worlds for learning and self-improving their performance. Humans are able to make heuristic judgments and take decisions, thus human intelligence is an essential part of any CPS. These collaboration between artificial and human intelligence is essential for the correctness of the CPS. Finally, simulating the physical world can reduce the costs, efforts and time of developing CPSs. Assistant training from virtual reality, for instance, is the base training of every future pilot. A recent study on CPSs, includes military, aerospace, communication and automotive sectors has shown the increasing usage of Field-

Fig. 2.1 Cyber-Physical System

Programmable Gate Array (FPGA) in simulating embedded systems. Moreover, the FPGA market value in these sectors is growing over 9% from 2014 to 2020 [Inc15].

### 2.1.1 Classification of Real-time Systems

Real-time systems can be classified from different perspectives. Classifications that are relevant for this thesis are presented in this subsection.

A real-time system must execute its services based on the collected inputs and calculate its outputs within bounded time intervals. The time instant at which an output must be produced by the system is called *deadline*. Real-time systems with at least one hard deadline that has to be met are called *hard real-time systems* or *safety-critical systems* [Kop97]. The

Fig. 2.2 Decision making in cyber-physical systems

design of hard real-time systems requires guaranteed temporal behavior under specified load and fault restrictions. On the other hand, in case no hard deadlines are declared, the system is called *soft real-time system* and deadlines are allowed to be missed occasionally. *Firm real-time systems* are systems where deadline misses are tolerable but this may reduce the system's utility.

In case of hard real-time systems, the ability of reacting to a failure determines whether the system can be called fail-safe or fail-operational. If the system can reach a safe state quickly in case of such a failure then it is called *fail-safe* system. For instance, a traffic light at a busy cross road can be set to red in case of a failure in the traffic control system. On the other hand, systems that have to stay operational regardless of possible failures are *fail-operational* systems, e.g., the flight management system of an airplane.

Another classification of real-time system is the classification with respect to the type of the temporal control signals of the system. A *trigger* in a real-time system is a stimulus that causes the start of an action. Triggers can be initiated in one of the following two ways, using event-triggered or time-triggered control signals.

*Event-triggered* control signals are not necessarily bound to timing events. Significant events can be any relevant state changes e.g., receiving a specified message. An event-

triggered system handles these events based on interrupts to serve the event accordingly. On the other hand, all communication and processing activities in *time-triggered* systems are initiated periodically based on a priori known clock ticks. Clocks of the distributed time-triggered system are synchronized based on a global time base, as will be explained in section 2.3.

### 2.1.2 Distributed Real-time System Model

The notion of real-time can be extended to the levels of operating systems, communication networks and scheduling. In this dissertation we are mainly focusing on the real-time communication and its design decisions.

Distributed real-time systems are composed of a set of computational nodes that are connected though a real-time communication network to control the functions of a controlled object. This model structure requires the definition of two interfaces, the so-called manmachine interface (e.g., keyboard, touch screen) between the operator and the real-time computer system. Secondly, the instrumentation interface is located between the controlled object and the real-time computer system. This interface converts physical signals of the sensors and actuators to digital forms in both directions.

The sequence of the results over time is called the distributed real-time system's *behavior*. Based on that, a *behavioral model* defines the behavior of a real-time system. A behavioral model can be defined using components, states and messages.

A *component* is a unit built on hardware and executes a software application that performs well-defined function within a larger system. The behavior of the component is defined in terms of interfaces from and to the component. The behavioral model contains a composition of computational components that implement specified functions, exchange messages and alternate between the system's states to produce results. During a component execution, all past information that can be accumulated at a given instance is called *state*, and this information is directly relevant to upcoming operations of the component. Furthermore, the change of the state is called an *event* [OK05].

A *message* in the behavioral model is a data structure that contains a number of data fields with dedicated names. These fields comprise semantics of the message such as source, destination, priority and payload. Moreover, data exchange via shared memory is also a means of communication.

*Interfaces* are needed in large system in order to provide functional and temporal abstractions between the different components of the distributed system. There are many types of interfaces depending on the purpose of the interface, i.e., Technology Independent Control

Interfaces (TIIs), Technology Dependent Debug Interfaces (TDIs), linking interfaces and local interfaces [Kop13].

Linking Interfaces (LIF) entail operational and meta-level specifications of the intercomponents communication. This includes the structure of the exchanged messages, and the temporal details for the messages. This represents the operational specification of the syntactic and temporal properties accordingly. The semantics of the message are described based on the meta-level specification of the interface. A component can provide LIF services and it can request linking services provided by other components. An example of such interface is the component interface to the communication network.

*Local interfaces* are responsible for providing the link to the external environment. However, the semantic content relevant for this interface is specified in the LIF.

Components that link the internal world of a cluster with the external environment are called *gateway* components. These components have two interfaces, a LIF that provides the link to the cluster's communication networks and a local interface that provides the link to the external environment. Network and memory gateways are good examples of gateway components.

### 2.1.3 Concept of Timing in Real-time Systems

The *granularity* of a time base is the duration between two consecutive micro-ticks in a digital physical clock.

Synchronization of the system activities requires the preservation of the time information related to the occurrence of an event or system activity. This can be established by attaching a dedicated time stamp to each of the activities. Time stamps are called *absolute* in case they are synchronized to a reference clock. A *reference clock* is an external clock that is detecting and observing all activities of the system as a timekeeper.

Assuming that we have a distributed system that consists of multiple nodes. Each node has its now local physical clock and all local clocks have the same granularity, and are synchronized with the same precision. The time *precision* is the maximum offset between the micro-ticks of two different clocks. As a result, a selected set of micro-ticks for each local clock can be considered as global ticks of the system's global time.

Clock synchronization is done at two levels, internally and externally. *Internal* synchronization ensures that the occurrence of all global ticks is always within the precision defined for the system. This is done by synchronization messages between the different nodes. Synchronization messages might be subject to a so-called malicious or Byzantine error, where such errors can easily result in inconsistency of the subsystem clocks. To resolve this

problem, either interactive-consistency algorithms or inconsistent algorithms with bounded effects of malicious clocks (e.g., fault-tolerant-average algorithm [LMS85]) are used.

External clock synchronization is responsible for aligning the global time ticks of the system to an external time standard, e.g. global positioning system. Time synchronization in this case is done through time gateways that are also responsible for the timely correct initialization of the system, as well as time-format mapping from one time standard to another one. Finally, the local time gateway is responsible for communicating and synchronizing with the other time gateways and executing time re-initialization when needed.

As discussed earlier, distributed real-time systems with time-triggered control have to be synchronized to establish a global time base for all time-triggered subsystems. Without clock synchronization, internal clocks of a set of subsystems may differ even if they have initially started accurately due to clock drifts [TS01]. Therefore, clock synchronization in distributed embedded systems is very essential. There are a number of existing solutions for clock synchronization, e.g., precision time protocol, global positioning system, Network Time Protocol, IEEE1588. Network Time Protocol (NTP) is a frequently used clock synchronization solution between computer systems. In previous work of the author, a distributed system based on time-triggered control was presented where NTP was used to provide clock synchronization [OAOD14].

#### **Timing Properties and Time Analysis**

It is essential that all time constrains and synchronization requirements of real-time embedded systems are met. Hence, timing models and analysis techniques are required to calculate and ensure the achievement of these time requirements. In the following, a number of timing properties that are used for embedded systems are discussed.

The *execution time* is the time required for a task or action within a component to finish after it has started [Zur09]. This measure cannot easily be derived as it inherently depends on the hardware and the execution flow of the system components and services. Execution time estimation provides more flexibility for system analysis. The WCET for instance, is a way to bound the execution time of a task or action. WCET approximation methods are important to deal with the unpredictability of present-day computing platforms (e.g., speculative execution, caches). [WEE+08].

The *response time* is the time calculated from the difference between the task completion time and its release time. The release time is the time when the task becomes ready for execution [But11]. The task response time must be bounded especially in hard real-time tasks. For instance, the required response time in control loops is often in the order of milliseconds or even less. System components involved in the time analysis might change

2.2 Dependability

based on the dependencies and interference within on the examined subsystem. For instance, the calculation of the response time in a system might include the network between the components. This depends on whether the network itself is considered autonomous or as part of the components.

The *end-to-end delay* at communication levels of an embedded system, is the time property that relates the occurrence of an event in time to the occurrence of another event. As an illustration, this delay in message-based systems is calculated from the time that a message requires to be transmitted from a source component to the delivery at its destination. This transmission could possibly include multiple networks such as on-chip and off-chip network interconnects [OOA<sup>+</sup>14b].

# 2.2 Dependability

There is a precise and rigorous terminology used in the literature to describe the basic concepts of dependable computing codified by Laprie [cLR01]. Based on that, the *dependability* of a computing system is its ability to deliver services that can justifiably be trusted. Additionally, dependability is defined by the *IFIP Working Group 10.4 on Dependable Computing and Fault Tolerance* as "the trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers". Alternatively, it was defined in *IEC IEV 191-02-03* as follows: "dependability is the collective term used to describe the availability performance and its influencing factors: reliability performance, maintainability performance and maintenance support performance".

### 2.2.1 Dependability Attributes

In the following subsection a number of key dependability attributes that have to be taken into consideration to deliver a dependable system are presented.

### Reliability

Reliability in embedded systems is defined as the continuity of the services. In other words, reliability is the ability of the systems to provide failure-free operations for a specified period of time in a specified environment. Based on this definition, a reliable service shall not fail for a given period of time, or it shall be able to successfully recover to a safe-state in case of a failure. This safe-state is a state that can be quickly identified in *fail-safe* real-time systems in case of a failure. Highly reliable embedded system services in safety-critical systems are demanded to exhibit failure rates are in the order of  $10^{-9}$  failures/hour [LHSC10].

### **Availability**

Availability is the probability of the system to be ready when needed, i.e., it is the system readiness to provide sufficient quality of service. Reliability and availability are directly connected. Therefore, the following reliability parameters are used in order to calculate availability.

$$Availability = MTBF/(MTBF + MTTR)$$

(2.1)

Availability is the rate of the estimated average time between failure of system components (known as Mean Time Between Failures (MTBF)) divided by the sum of the MTBF added to the average time needed to repair the failed system module (known as Mean Time To Repair (MTTR) [LS11]).

#### Safety

Safety is the avoidance of catastrophic consequences on the environment by avoiding critical failure occurrence. Such failures impose significantly higher cost than the utility of the real-time system. As a result, safety is a characteristic of the whole system and not only of a single component [Sto96]. For instance, one traffic light at a road junction can be set to "red" in case of a failure of the system, but this is not enough to avoid possible collisions. All traffic lights at the junction shall stay at "red". In order to design a safe system, safety shall be considered in the context of the system and not only at the component or the software levels. It is important to mention that the previous example can be called a safe system, but it is not necessarily a reliable one.

Different industry segments (e.g., automotive, avionic, medical) are demanding systems with specific safety features. Despite the size of investments in this area, designing truly safe systems is sill highly challenging. Modern cars contain a big number of embedded computing systems that are connected hierarchically. For example, these embedded systems exchange highly important inter-process messages relevant for advanced driver assistance systems (ADAS) in parallel with higher level infotainment and navigation messages that are of lower importance. Such a system, also known as a MCS, is required to react safely in case of faults.

MCSs consist of a number of subsystems that are sharing their communication and computational resources, where these subsystems have two or more different criticality levels. These levels are defined based on certification standards. The certification process is based on evidences that are established by activities such as documentation, reviews, audits or

testing. This includes the identification of the possible hazards, determine the risks and then defining the safety measures.

Safety standards have been evolving over the years, DINVVDE 0801, DINV 19250, EUROCAE-ED-12B, EN 954 and ANSI/ISA S84.01 are examples of standardization attempts for safety standards relating to computers in control [Col08]. Nowadays, IEC 61508 is a cross-domain functional safety reference that is widely used in the industry. Potentially, this standard can be extended to any other industrial domains, e.g., medical electrical equipment, trains, wind power. For instance, it has been extended to meet the functional safety requirement of the automotive domain (i.e., ISO 26262). The IEC 61508 standard requires risk assessment and hazard avoidance to be carried out in the whole system. This requires the definition of the so-called Safety Integrity Levels (SILs) of the system, which are the criticality levels of the system based on that standard. The demanded reliability in these four SILs in case of IEC 61508 can vary from 10<sup>-2</sup> to 10<sup>-1</sup> at low demand, up to 10<sup>-9</sup> to 10<sup>-8</sup> at high demand mode [Bel06].

### **Security**

The last attribute of dependability that we discuss is *security*. It is the ability of the system to prevent unapproved access to data or services including the reduction of vulnerabilities and protection against threats, attacks, interference and espionage [Gas88] [WLSC07]. Security attacks aim to obtain access to hardware, software, information and possibly to modify specific service functionality. *Threats* exist vertically at all levels of the system from hardware/physical level up to the operating system and application level. *Attacks* that results in these threats are usually categorized into the following main categories: backdoor, denial-of-service, direct-access, eavesdropping, spoofing, tampering, privilege escalation, phishing and click-jacking attacks. Attackers might attempt their attack on the computer systems or even on the users as in social engineering attacks.

The security issue of computer systems has been keeping engineers and researchers busy since the beginning of the digital system evolution. Therefore, a number of defense strategies have been developed, e.g., access control systems and application security using antivirus software. Despite the long list of defense options to obtain better secured systems, security remains a prevalent challenge in present day embedded systems. An example for the vulnerability of automotive systems was demonstrated by the automotive security researchers Charlie Miller and Chris Valasek. They hacked a Chrysler Jeep using a "wireless attack" at the Black Hat 2015 conference in Las Vegas. This hack has caused the recall of 1.4 million vehicles by the car manufacturer [Yos16].

#### 2.2.2 Faults and Fault Tolerance

Dependability and security threats are linked as described by Avizienis and Laprie [ALRL04]. They are divided into faults, errors and failures.

The *function* of a system is what the system is intended to do, as described by its functional specification. Faults occur often in systems such as a frozen memory bit, an uninitialized variable in software, or a cosmic ray ionizing its way through an embedded system. The ensuing failures indicate the disagreement between the defined service and the actual behavior in the system. An *error* is a system state that may lead to a failure. An error is detected if an error message or signal is produced within the system or latent if not detected. A *fault* is the cause of an error, and it is active when it results in an error, otherwise it is dormant. A system *failure* occurs when the delivered service does not comply with the specification.

The cause of faults is vary diverse, hence they are classified into three major classes. Firstly, *design faults* can occur at both hardware and software levels. It can be due to software flaws or due to hardware errata. Moreover, the erroneous logic can appear upon the integration of both hardware and software of the system. The second class of faults are the *physical faults*. This type of faults is non-human made, which means that they exist due to product defects or physical damage of the system. Finally, malicious attacks or faulty inputs in addition to possible physical interference can result in *interaction faults*.

Fault-tolerance is the ability of a system to preserve its ability to deliver a correct service in the presence of faults [ALRL04]. The ability to detect and process error states and assess the consequences is essential for having a fault-tolerant design. This is achieved by removing system error states, and then treating the source of the fault. Our goal as engineers is to prevent the occurrence of system failures in our embedded systems, which requires a well defined process. Therefore, quality control techniques at both software and hardware levels shall be applied. Each class of faults has its own techniques to prevent failures and acquire its means to achieve the dependability of the system. Model-based and object-oriented design for instance are introduced to prevent software design faults and consequently failures. In distributed systems failures caused by such faults can propagate from a system to another one through a message failure in the time or value domain. Therefore, proper design decisions have to avoid this propagation, using proper network interfaces as in [OKSH07]. Moreover, radiation hardening and foolproof packages are used to mitigate physical faults and interaction faults [cLR01].

*Error containment* is the ability of the system to handle errors. This can be performed in two phases, error handling and fault handling. Identifying and saving specific safe states (so-called checkpoints) of the system can help to rollback to points in time where the system

was free of that error. Such an *error handling* technique for eliminating errors is used in distributed shared memory systems [JF95]. What is important in *fault handling* is to identify the cause of the error and isolate the faulty component of the system, which can be a software component or a hardware component.

Software and hardware fault tolerance is achieved by using redundancy [KK07]. Hardware redundancy techniques often make use of multiple identical components or subsystems, in addition to means for arbitrating the resulting output, e.g., majority voting. ECC memory, for example, uses a few extra bits to detect and correct errors resulting from faults in the individual storage bits. Running the same input data through a faulty software module multiple times yields the same erroneous result each time. Redundancy can be done by 1-to-1 redundancy or up to N redundant instances. However, Triple Modular Redundancy (TMR) is commonly used in both software and hardware fault tolerance.

Software fault tolerance is built by applying algorithmic diversity, computing results through independent paths, and by judging the results. This adds complexity to the system in general. Adding software fault tolerance will improve system reliability only if the gains made by the added redundancy are not offset by commensurate new faults introduced by the redundant parallel code. In case of N-modular redundancy in hardware fault tolerance, the cost of the system health monitoring for all instances is very high. Therefore, a hierarchical structure of health monitoring units can be applied.

Based on Kopetz [Kop06], the following instructions have to be followed in order to establish a fault-tolerant system. Initially, assumptions must be specified for the types and numbers of faults that will be tolerated in the designed system. This is called the phase of the fault hypothesis. The definition of specific Fault Containment Regions (FCRs) is part of this phase. An FCR is the set of components or subsystems that shares one or more common resources that can be affected by a single fault and is assumed to fail independently from other FCRs of the system. Moreover, it is mandatory to identify specified failure modes for each FCR at this phase. Each single FCR in the designed embedded system can fail in a specific failure mode, e.g., fail-stop, crash, omission, timing, byzantine or babbling idiot [Kop05]. The design phase is the second phase of the process, taking into account the previous assumptions. Finally, the designed architecture can be implemented and validated using the selected fault-tolerance mechanisms and the fault hypothesis that was assumed.

# 2.3 Paradigms of Communication

#### 2.3.1 Shared Memory and Messages-based Communication

The increasing number of cores integrated on a single chip has introduced the need for efficient inter-core communication means. These means are used to exchange data and provide access to the required memory resources. Cores might share specific data blocks with other components, where this data shall be exchanged concurrently.

In multi-core embedded systems, memory data is usually shared and distributed between local caches at the cores and external memories. Each core will have its corresponding memory segments (locally or remotely). Moreover, data can be exchanged between the cores though a shared memory by employing overlapping memory segments. Shared memory-based communication requires the support of a hierarchical memory architecture and concurrency algorithms (i.e., cache coherency protocols, cf. Section 2.4.1). This type of communication is more expensive from the overall execution time point of view, and has a high hardware complexity.

In case of message-based communication, a message structure is defined to wrap all needed information for data exchange between the cores. Message-based communication ease of use for application developers, it involves better utilization from a bandwidth point of view, and it typically provides better spacial isolation between the components. It can also be easily managed to provide better timing isolation in combination with a TDMA communication scheme, as will be explained later.

These two forms of communication can be combined to benefit from both paradigms as described in this dissertation.

# 2.3.2 Event Triggered vs. Time Triggered Communication

An overview of the different types of control paradigms is discussed in this subsection. Control signals in embedded systems are initiated when an action occurs, such as, a transmission of a message, the start of a service, or a memory request. As discussed in previous sections, embedded systems can be classified based on their control signals into event triggered and time triggered systems. This differentiation depends on the source of the triggers.

In case control signals are generated based on events then we are talking about *event triggered communication*, where every change of the system state is considered as an event [Kop13]. This event might be generated internally within the real-time system, or it might be originated from one of the controlled objects of the real-time system. A good example of event triggered communication is the CAN bus that is widely used in the chassis

control systems and power train communication [Amo04]. An event message is a message that contains event observations of the difference between the last observed state and the new state. The notion of time in such messages denotes the point of time at which the state has changed. Communication guarantees in event triggered real-time systems are provided by using control flow protocols with some sort of acknowledgment. Positive Acknowledgment with Re-transmission (PAR) for instance, is one of the control flow protocols using positive acknowledgment for successful reception of the message. The usage of such protocols provides resilience against transient failures in event triggered systems. The basic idea of PAR is very simple, each sender has a predefined time-out to receive the reception acknowledgment from the receiver. In case, the time-out is over without the reception of the acknowledgment, the sender attempt to re-transmit the message considering that some failure occurred in the reception of the previous attempt. Moreover, explicit control flow can be used to solve timing failures, where the receiver can send a control signal to inform the sender about its desire to send another message [OK05]. Generally, PAR based communication protocols (e.g., TCP/IP) are not considered as suitable for safety-critical systems.

In case of time triggered communication, the communication activities are periodically triggered and synchronized based on a global time base. If multiple components in a real-time system are observing each other, then the observed events shall have the same temporal order in all components. Therefore, all control signals are generated in restricted and particular points in time in relation to the global time based on the a priori knowledge of the real-time system. The task period, the phase, the sender component and receivers are examples of the a priori knowledge. Time triggered communication provides deterministic behavior and guarantees high temporal predictability and composability of the real-time system.

Event-triggered protocols such as Ethernet and CAN do not provide sufficient guarantees with respect to timeliness and reliability in safety-critical systems. However, a communication control strategy is needed to provide temporal control and avoid conflicts between messages. As explained by Lee in [LLS07], safety-critical systems typically use static TDMA-based protocols, e.g., TTP/C or FlexRay. TDMA defines the time-based communication scheme that is used by the communication controller of each component to disseminate the messages. The communication scheme is defined by dividing the capacity of the communication channel is statically divided into a number of slots. Each slot is dedicated for a certain component of the real-time system. Each component has it own sequence of sending slots in the so-called TDMA round. The completion of the TDMA rounds of all components denotes the cluster/system cycle that is periodically repeated. The resulting static schedule defines the communication between all components of the system with respect to the global time. Additionally, a priori knowledge of the system (e.g., the number of components, sending time,

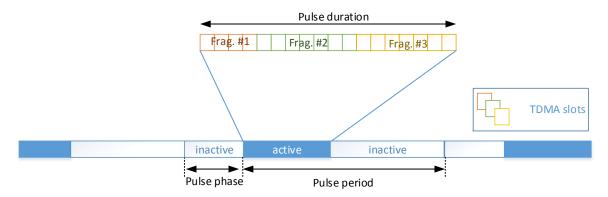

Fig. 2.3 TDMA-Pulsed Data Stream [OESHK08]

receiving time, etc) is required. Finally, message handling is done at design time without any need for explicit control flow as in event triggered communication systems.

In Time-Triggered Ethernet (TTE) [Obe11], frames are based on Ethernet as standardized in IEEE 802.3. To start the communication, Pulsed Data Streams (PDSs) specify the carrying signals and their clock pulses. A PDS is a time triggered, periodic, uni-directional data stream, which is identified by periodic pulses with defined pulse period and defined pulse phase. As illustrated in Figure 2.3, at least one fragment of variable size construct the PDS and the fragments of a PDS do not require to be transmitted without interruption. The time between the start of the transmission of the first fragment and the end of the transmission of the last fragment is known as the duration of the pulse. The phase of the pulse is the offset until the transmission is started. Each fragment is composed of a set of fixed-size flits.

# 2.3.3 Types of Communication Messages

Communication activities in real-time systems are initiated at specific points of time (cf. Section 2.1.3). Moreover, three message types can be distinguished in real-time systems: periodic, aperiodic and sporadic messages. Determinism and real-time support in time triggered communication requires *periodic message* exchanges, where messages contain the absolute real-time value. These periodic messages are transmitted at predefined points in time, with a specified period and phase, according to a communication schedule. The communication of periodic messages can be planned at development time in order to minimize latency and jitter. Finally, message queuing is not required at the communication interfaces in time triggered communication, since real-time applications are interested only in the most recent value of the observed object.

Messages with unspecified bit rate and delivery timing constrains are called *aperiodic* messages. This type of messages is typically served based on the current traffic load of the network. Namely, these messages use the remaining bandwidth of the network to be

transmitted. Hence, there are no guarantees for the transmission or receiving of the message. Additionally, possible delays or even message loss might occur.

Sporadic messages (a.k.a., rate-constrained messages) are messages with bounded minimum interarrival times. The total allocated bandwidth is calculated from the bandwidth allocation gap (BAG), and shall not exceed the maximum available bandwidth. Although rate-constrained messages are suitable for real-time applications (e.g., ARINC-664P7/AFDX [TPS15]), sporadic messages are determined for less stringent communication constrains than the periodic messages.

# 2.4 Memory Technologies and Hierarchy

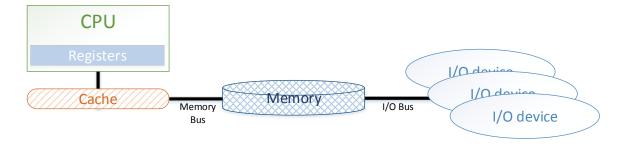

Memories are one of the main components comprised in all embedded systems. Nowadays, computational components are becoming faster and more numerous. Moreover, the performance and size of memory is growing due to the low cost. The real limitation factor in embedded systems is memory efficiency and memory access. Existing memory handling approaches, both in software and hardware, promise to provide higher efficiency for memory architectures in embedded systems. Figure 2.4 shows a typical memory hierarchy in a single processor core. It is important to mention that the cost for data fetching is increasing dramatically as much as location of the required data away from the requesting processor. This expansion can be noticed in larger scale memory architectures in distributed systems. Cross-cutting system-level issues e.g., performance and reliability [JNW07] become much more complex to manage and handle at that level.

Fig. 2.4 Typical memoy hierarchy in embedded systems

The following characteristics are used to classify memories. The *capacity*, i.e., the global volume of information that the memory is able to store can be in the order of gigabytes or even terabytes (e.g., the world's largest hard drive is 16 TB [Mos16]). Secondly, the *access time* corresponds to the time interval between the read/write request and the availability of the data. Third, the *memory cycle* time represents the minimum time interval between two

successive accesses. Fourth, the *throughput* defines the volume of information exchanged per unit of time, expressed in bits per second. Finally, memories are characterized based on their ability to retrieve the stored digital data after being switched off and on again. Magnetic tapes, mechanical drives, solid-state drives, flash memories and different forms of Read-only Memory (ROM) belong to the *non-volatile memories*. This type of memories is able to store information over long term, and stored data is not lost after power down. The second type of memories is called *volatile memory*, where stored data will be irremediably erased in case of power down. Volatile memories such as general purpose RAM including dynamic and static RAMs are directly accessible to the computational cores (CPUs) using the memory bus. This bus comprises an address bus and a data bus. In case that a memory instruction is triggered, the desired memory address is sent through the address bus, then the data for the read (or write) request is sent through the data bus.